A Deep Dive on Digital Systems: Exploring Topics within the FE Electrical Exam Pt. 2

Welcome back to the topic of digital systems! We will continue where we left off and explore flip-flops and counters, programmable logic devices and gate arrays, state machine design, and timing (e.g., diagrams, asynchronous inputs, race conditions, and other hazards).

In this Blog,

1. Flip-flops and Counters

2. Programmable Logic Devices and Gate Arrays

3. State Machine Design

4. Timing

5. Conclusion

2. Programmable Logic Devices and Gate Arrays

3. State Machine Design

4. Timing

5. Conclusion

Flip-flops and Counters

Flip-flops are edge-sensitive devices that are controlled by clock transitions. Their behavior and output depend on the rising or falling edges of the clock signal. Incorporating flip-flops into a circuit also adds state properties to the circuit, meaning the output relies not only on the current input of the system but also on its previous inputs.

A flip-flop is a sequential logic device. Thus, it has two possible output states: 0 or 1. Another contributing attribute to the output is that it is synchronized with a clock signal (CLK), ensuring that changes in the output should occur at specific clock time intervals. The signal Qn represents the value of the flip-flop's output before the application of the CLK signal, while Qn+1 represents the output value after the CLK signal has been applied. There are 3 basic flip-flops that you need to know for the FE exam: D flip-flop, SR flip-flop, and JK flip-flop.

1.D Flip Flop

Figure 1

Figure 1

The master-slave flip-flop exhibits distinct characteristics in its operation. A change to the input, D, will affect the “Master D latch”, while the slave output shall remain unchanged. As the clock pulses back to 0, the master section will be disabled, isolating it from the D input; simultaneously, the slave section then becomes enabled.

This change in master influence allows the value of Y to be transferred to the flip-flop's output at Q. Notably, a change in the flip-flop's output can only be triggered during the transition of the clock from 1 to 0, providing precise timing control for the circuit's behavior (Widmer et al., 2017, 260-261).

The truth table for the D flip-flop is shown below:

|

D |

Qn+1 |

|

|

0 |

0 |

Reset |

|

1 |

1 |

Set |

The characteristic equation is depicted below

Qn+1 = D

2. SR Flip Flop

SR flip flop stands for Set Reset flip flop. SR flip-flop (Figure 2) is constructed with the use of a NAND latch and two NAND gates (Widmer et al., 2017, 256).

Figure 2

The truth table for SR flip-flop is shown as below

|

S |

R |

Qn+1 |

|

|

0 |

0 |

Qn |

No change |

|

0 |

1 |

0 |

Reset |

|

1 |

0 |

1 |

Set |

|

1 |

1 |

Indeterminate |

Indeterminate |

The characteristic equation is depicted below:

Qn+1= S + QnR'

3. JK Flip Flop

The JK flip-flop can be seen as the improved iteration of a SR flip-flop; its design addresses the issue of an indeterminate state that arises when both inputs of the SR flip-flop are set to 1 (Widmer et al., 2017, 258).

In the JK flip-flop:

- The J input functions similarly to the S input of the SR flip-flop, intended to set the flip-flop to a particular state.

- The K input behaves akin to the R input of the SR flip-flop, responsible for resetting the flip-flop and changing its state (Widmer et al., 2017, 259).

The logic circuit of a JK flip-flop (Figure 3) is built by utilizing an SR flip-flop that is itself constructed from a NAND latch (Widmer et al., 2017, 259-260).

Figure 3

The truth table for JK flip-flop is shown as below: The characteristic equation is depicted below

|

J |

K |

Qn+1 |

|

|

0 |

0 |

Qn |

No change |

|

0 |

1 |

0 |

Reset |

|

1 |

0 |

1 |

Set |

|

1 |

1 |

Q'n |

Compliment |

The characteristic equation is depicted below:

Qn+1= JQ' + K'Q

Programmable Logic Devices and Gate Arrays

1. Programmable Logic Devices (PLD)

PLDs, also known as field-programmable logic devices (FPLDs), offer the flexibility to create a wide range of digital circuits, from simple logic gates to complex digital systems.

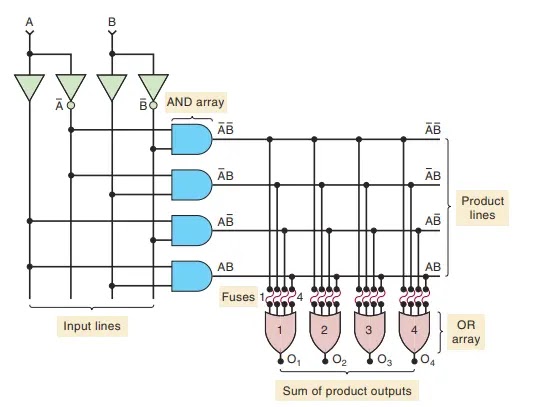

With the understanding that any function can be expressed in sum-of-product (SOP) form, a programmable logic device (PLD) is composed of the following components (Widmer et al., 2017, 948):

- Input buffers and inverters generate both the original and complement forms of each input variable.

- A set of AND gates, where the inputs can be programmed or selected.

- A set of OR gates, where the inputs can also be programmed or selected.

Figure 4

Example:

.webp)

Figure 5

Write the functions of f1 and f2 for the PLD above?

We just need to carefully examine which input and out are being connected to the gate.

f1 = x1x2 + x1x3' + x1'x2'x3

f2 = x1x2 + x1'x2'x3 + x1x3

2. Gate Arrays

Gate arrays are highly integrated circuits with a vast number of gates, often numbering in the hundreds of thousands. These devices rely on pre-fabricated gates that are interconnected to create the desired logic functions. The gate interconnections are determined by a custom-designed mask specific to the application, similar to the data stored in a mask-programmed read-only memory (ROM). Due to this characteristic, gate arrays are sometimes referred to as mask-programmed gate arrays (MPGAs) (Widmer et al., 2017, 943). While individually less expensive than PLDs with a similar gate count, gate arrays require custom programming, which adds complexity to their implementation.

State Machine Design

A state machine refers to a mathematical model or an abstract machine that exhibits different states and transitions between those states based on input conditions. It is a fundamental concept used to design and control sequential logic circuits.

A state machine consists of a finite set of states, a set of inputs, a set of outputs, and a set of transitions that define the behavior of the machine. The current state represents the internal condition of the machine, and the transitions determine how the machine moves from one state to another in response to input signals (Widmer et al., 2017, 481).

Let’s take a look at this flip flop circuit (Figure 6).

Figure 6

To construct a state diagram of Figure 6, the following steps need to be followed:

- Obtain the function of the circuit: Understand the behavior and logic of the system to define its function.

- Determine the four main components: Identify the present state, inputs, next state, and output of the circuit. These components define the behavior and transitions within the system.

- Create a truth table: Combine the function and the four components to form a truth table. The truth table represents all possible combinations of inputs and current states, along with the corresponding outputs and next states.

- Obtain the binary result: Analyze the truth table to determine the binary representation of the system's behavior and transitions. This binary result serves as the foundation for constructing the state diagram.

The equation for this flip-flop is an XOR function, and the truth table is constructed below.

A (t+1) = A x y

|

Present state |

Inputs |

Next state |

|

|

A |

x |

y |

A |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

.webp)

Figure 7

We see that this state machine uses a single flip-flop. Therefore, it has two distinct states. Looking at the state diagram (Figure 7), these two states are represented as two circles, and the arrows indicate which input combination allows the current state to change from one to the other. The number inside the circles indicates that both the present state and the output can be either 0 or 1. For each state, the two inputs can assume four potential combinations.

Timing

A timing diagram is a visual representation of a set of signals in the time domain, usually consisting of a clock signal and an input and output.

The use of timing diagrams helps to find and diagnose digital logic hazards: Static, Dynamic, and Function Hazards. Logic Hazards are undesirable effects caused by either a deficiency in the system or external influences on the system (University of Surrey, n.d.). This can occur when changes in the input variable(s) do not change the output correctly.

- Static Hazards are when one input variable changes the output changes momentarily.

- Dynamic Hazards are when an output changes more than once from a single input change.

- Function Hazards are when more than one input variables change at the same time.

Conclusion

Through this two-part blog series, I have offered concise explanations for each digital systems topic found on the FE Electrical exam. If you are looking for more comprehensive exam prep, check out School of PE’s FE Electrical exam review course!

References

Widmer, N. S., Tocci, R. J., & Moss, G. L. (2017). Digital Systems: Principles and Applications. Pearson.